# Fundamentals of Microprocessor and Microcontroller Course Material (EC-223)

Prepared by: Er. Vivek Harshey Assistant Professor (ECE)

Department of Electronics and Communications Engineering

Sant Longowal Institute of Engineering and Technology

(Deemed to be University)

Longowal-148106, Sangrur, Punjab

# **CONTENTS**

| CHAPTER 1. INTRODUCTION TO MICROPROCESSORS                  | 5  |

|-------------------------------------------------------------|----|

| 1. Relevance of 8-bit Microprocessors in Academic Education | 5  |

| 2. THE MICROPROCESSOR AS A PROGRAMMABLE DEVICE              |    |

| 3. ORGANIZATION OF A MICROPROCESSOR-BASED SYSTEM            | 9  |

| 4. MICROCOMPUTER ORGANIZATION:                              | 12 |

| 5. Memory                                                   |    |

| 6. Microcomputer Bus System                                 |    |

| CHAPTER 2. 8085 ARCHITECTURE AND PIN DIAGRAM                | 19 |

| 1. Internal Architecture of 8085                            | 19 |

| 2. PIN DIAGRAM AND FUNCTIONS OF VARIOUS PINS                |    |

| 3. System Bus (Address Bus, Data Bus, and Control Bus)      | 24 |

| 4. DATA FORMATS IN COMPUTER                                 |    |

| 5. HARDWARE COMPONENTS IN A MICROCOMPUTER-BASED SYSTEM      | 26 |

| CHAPTER 3. THE 8085 INSTRUCTION SET                         | 29 |

| 1. Addressing Modes Available in 8085                       | 29 |

| 2. Classification of 8085 Instructions                      |    |

| CHAPTER 4. MEMORY AND I/O INTERFACING                       |    |

| 1. Memory Classification                                    |    |

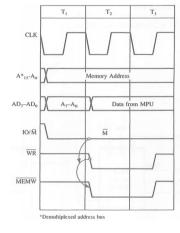

| 2. MEMORY READ MACHINE CYCLE                                |    |

| 3. Memory-Write Operation                                   |    |

| 4. REQUIREMENTS OF A MEMORY CHIP AND MICROPROCESSOR BUS     |    |

| 5. Interfacing of $1K$ ( $1024 \times 8$ ) memory           |    |

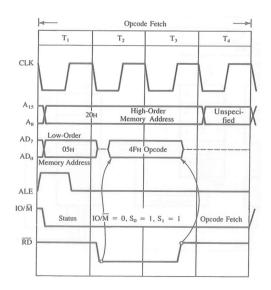

| 6. TIMING DIAGRAM FOR OPCODE FETCH OPERATION                |    |

| 7. MEMORY-MAPPED I/O AND I/O-MAPPED I/O SCHEMES             |    |

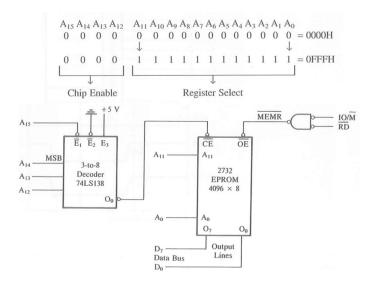

| 8. Interface a 2732 EPROM (4K bytes) memory chip            |    |

| 9. COMPARISON OF MEMORY-MAPPED I/O AND PERIPHERAL I/O       |    |

| CHAPTER 5. 8085 PROGRAMMING MODEL                           |    |

| 1. Programming Model                                        | 49 |

| 2. Instruction Classification                               |    |

| 3. Instruction Format and Examples                          |    |

| 4. Arithmetic Instructions in 8085                          |    |

| 5. Increment Instructions In 8085                           |    |

| 6. SIMPLE ASSEMBLY LANGUAGE PROGRAMS FOR 8085               |    |

| CHAPTER 6. 8051 MICROCONTROLLER                             |    |

| 1. Introduction to the 8051 Microcontroller                 | 58 |

| 2. Architecture of the 8051 Microcontroller                 |    |

| 3. I/O Ports in 8051 Microcontroller                        |    |

| 4. Basic Concept of Memory in 8051                          |    |

| 5. Basic Instructions in 8051 Microcontroller               |    |

| 6. SIMPLE PROGRAMS FOR THE 8051 MICROCONTROLLER             |    |

| Multiple Choice Questions                                   |    |

| Short Answer Questions                                      |    |

|                                                             |    |

| Descriptive Type Questions                                  | 79 |

## **PREFACE**

In the rapidly evolving field of electronics and embedded systems, a solid foundation in microprocessors and microcontrollers is essential for students in diploma and engineering disciplines. The  $8085\mu p$  and  $8051\mu c$  have been fundamental to studying digital electronics, providing students with a deep understanding of processor architecture, programming techniques, and interfacing concepts. Their simplicity and ease of implementation make them an ideal starting point for students stepping into microprocessor-based system design.

This course material and question bank have been designed as a learning resource, enabling students to grasp core concepts, strengthen problem-solving skills, and reinforce theoretical knowledge through structured questions. The document is intended to support students in preparing for academic exams, tests, and practical applications by covering the essential topics in a well-organized manner. This course material and question bank will function as a self-study guide, a reference document, and a revision tool for students. I sincerely appreciate feedback and suggestions for improvement, as continuous enhancement is key to better learning experiences.

Happy Learning!

Vivek Harshey

Asst Professor

ECE Deptt.

# **Syllabus**

|                                                                                                                                                                                                                                                                                                                                                 |         |                                                                                                                                                                                                                                                                                                                                                        |           |          |           | EC-223  |           |          |         |           |          |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-----------|---------|-----------|----------|---------|-----------|----------|----------|

|                                                                                                                                                                                                                                                                                                                                                 |         | ]                                                                                                                                                                                                                                                                                                                                                      | Fundam    | entals   | of Micro  | oproces | ssor & N  | Microco  | ntrolle | r         |          |          |

|                                                                                                                                                                                                                                                                                                                                                 |         |                                                                                                                                                                                                                                                                                                                                                        | I         |          |           |         | Γ         |          | P       |           | Cre      | edits    |

|                                                                                                                                                                                                                                                                                                                                                 |         |                                                                                                                                                                                                                                                                                                                                                        | 3         | 3        |           |         | 1         |          | 4       |           |          | 6        |

|                                                                                                                                                                                                                                                                                                                                                 |         | Session                                                                                                                                                                                                                                                                                                                                                | nal Mark  | XS .     |           |         |           |          |         |           | 5        | 50       |

|                                                                                                                                                                                                                                                                                                                                                 |         | End Se                                                                                                                                                                                                                                                                                                                                                 | mester l  | Examina  | ation Ma  | ırks    |           |          |         |           | 5        | 50       |

| Course<br>Object                                                                                                                                                                                                                                                                                                                                | _       | The objective of the course is to expose the students to the evolution of microprocessors, the architecture and instruction set of typical 8-bit microprocessor 8085. It also deals with Assembly Language Programming and input-output techniques. Next focus is to introduce the architecture, programming and interfacing of 8051 microcontrollers. |           |          |           |         |           |          |         |           |          |          |

| Course                                                                                                                                                                                                                                                                                                                                          | e       |                                                                                                                                                                                                                                                                                                                                                        |           |          | olution o |         |           |          |         |           |          |          |

| <ul> <li>Outcomes:</li> <li>2. Analyze the architecture of the Intel 8085 microprocessor and 8051 microcontroller for its various applications.</li> <li>3. Apply the programming techniques in designing simple assembly lang programs for solving simple problems by using instruction sets of microprocessor and microcontroller.</li> </ul> |         |                                                                                                                                                                                                                                                                                                                                                        |           |          | langua    | ge      |           |          |         |           |          |          |

|                                                                                                                                                                                                                                                                                                                                                 |         | 4. Use                                                                                                                                                                                                                                                                                                                                                 | the ado   | dressing | modes     | and tim | ing diag  | gram for | execut  | ing prog  | ram effi | ciently. |

|                                                                                                                                                                                                                                                                                                                                                 |         | l                                                                                                                                                                                                                                                                                                                                                      | Mappin    | g of cou | irse out  | comes v | vith pro  | gram ou  | itcomes | <u> </u>  |          |          |

|                                                                                                                                                                                                                                                                                                                                                 | P01     | P02                                                                                                                                                                                                                                                                                                                                                    | P03       | P04      | P05       | P06     | P07       | P08      | P09     | P010      | P011     | P012     |

| CO1                                                                                                                                                                                                                                                                                                                                             |         | ✓                                                                                                                                                                                                                                                                                                                                                      |           | ✓        | ✓         |         |           |          |         |           |          |          |

| CO2                                                                                                                                                                                                                                                                                                                                             |         | ✓                                                                                                                                                                                                                                                                                                                                                      | ✓         | ✓        |           |         |           |          |         |           |          |          |

| CO3                                                                                                                                                                                                                                                                                                                                             |         | ✓                                                                                                                                                                                                                                                                                                                                                      | ✓         | ✓        | ✓         |         |           |          |         |           |          |          |

| <b>CO4</b>                                                                                                                                                                                                                                                                                                                                      |         | ✓                                                                                                                                                                                                                                                                                                                                                      | ✓         |          | ✓         |         |           |          |         |           |          |          |

|                                                                                                                                                                                                                                                                                                                                                 |         |                                                                                                                                                                                                                                                                                                                                                        |           |          | Unit-I    |         |           |          |         |           | 1        | l4 hrs.  |

| Introd                                                                                                                                                                                                                                                                                                                                          | luction | : Typica                                                                                                                                                                                                                                                                                                                                               | l organi: | zation o | f a micr  | ocompu  | iter syst | em and   | functio | ns of its | various  | blocks.  |

**Introduction:** Typical organization of a microcomputer system and functions of its various blocks, Microprocessor, its evolution, function and its applications

<u>Introduction to 8-bit Microprocessor Architecture</u>: Concept of Bus, bus organization of 8085, functional block diagram of 8085, functions of each block of 8085 architecture, in details of 8085 and related signals.

Unit-Il 8hrs.

**Memories and I/O Interfacing**: Memory organization, concept of memory mapping, partitioning of total memory space, address decoding, concept of I/O-mapped I/O and memory mapped I/O. Basic Concept of RAM, ROM, PROM, EPROM and EEPROM.

Unit-Ill 12hrs.

**Programming using 8085 Microprocessor:** 8085 programming model, brief ideas of machine and assembly languages, machines and mnemonic codes, basic idea of instruction format and addressing modes, basic concept of instruction set for data transfer group, arithmetic group, logic group, stack, subroutine, I/O and machine control group, writing assembly language programs

Unit-IV 14hrs.

**Introduction:** Difference between Microprocessor & Microcontroller, Concept of Embedded System.

<u>Architecture of 8051 Microcontroller</u>: Architecture of 8051, I/O ports in 8051, basic concept of memory in 8051, basic idea of addressing Modes in 8051, basic idea of instructions in 8051, applications of microcontroller.

| BOOKS RECOMMENDED                                                          |                  |                                                 |  |  |  |

|----------------------------------------------------------------------------|------------------|-------------------------------------------------|--|--|--|

| Title                                                                      | Author           | Publisher                                       |  |  |  |

| l. Microprocessor Architecture- Programming & Applications with 8085/8080A | Ramesh S Gaonkar | 5th Edition, Penram<br>International Publishing |  |  |  |

| 2. Introduction of Microprocessors & Microcomputers                        | Ram B            | 4th Edition, Dhanpat Rai<br>Publisher (P) Ltd.  |  |  |  |

| 3. The 8051 Microcontroller                                                | Kenneth J. Ayala | 3rd Edition, Cengage<br>Learning, 2004          |  |  |  |

A microprocessor is a programmable electronic chip with computing and decision-making capabilities similar to a computer's central processing unit (CPU). A system built around a microprocessor with limited resources is referred to as a microcomputer. Today, microprocessors are embedded in nearly all electronic devices, including mobile phones, printers, washing machines, and home automation systems. Additionally, they play a critical role in advanced applications such as radar systems, satellites, and aerospace technology. The rapid advancement of the electronics industry and the development of large-scale integration (LSI) technology have led to significant cost reductions and increased adoption of microprocessors across various fields. A microprocessor is an integrated circuit (IC) that incorporates arithmetic, logic, and control circuitry, enabling it to interpret and execute instructions. As the core processing unit of a computing system, it facilitates the execution of computational and control tasks by coordinating with memory, input/output devices, and other peripherals. These interactions allow the microprocessor to execute operations as defined by user programs or system software, making it a fundamental component of modern digital and embedded systems.

Advancements in microprocessor technology have resulted in improved clock speeds, reduced power consumption, and increased integration of functionalities such as floating-point arithmetic, cache memory, and multiple cores. Modern microprocessors now support parallel processing and artificial intelligence capabilities, making them integral to various applications, from personal computing to industrial automation and embedded systems. One of the significant advantages of the 8085 microprocessor is its built-in serial communication capability, which facilitates data exchange between the processor and peripheral devices. It also includes five hardware interrupt signals and eight software interrupts, enabling efficient handling of external and internal events. Additionally, the 8085 supports both memory-mapped and I/O-mapped input/output operations, making it versatile for various interfacing applications.

The 8085 microprocessor is an 8-bit microprocessor developed by Intel in 1976. It has a 16-bit address bus, allowing it to address 64KB of memory. It operates on a +5V power supply and has a clock speed of 3 MHz. 8085 follows the von Neumann architecture, meaning both data and instructions share the same memory. It includes 74 instructions and supports five hardware and eight software interrupts.

# 1. Relevance of 8-bit Microprocessors in Academic Education

Despite the availability of 32-bit and 64-bit microprocessors, the 8-bit microprocessor remains a highly suitable choice for teaching microprocessor concepts, even in the twenty-first century. A significant reason for this is the widespread use of 8-bit microprocessors in industrial applications. Over 90% of microprocessor sales worldwide are accounted for by 8-bit processors and single-chip microcontrollers. These processors have firmly established themselves in industrial control systems, including machine control, process control, instrumentation, and consumer appliances. Such systems, incorporating microprocessors, are classified as embedded systems or microprocessor-based products.

In contrast, 32-bit and 64-bit microprocessors are primarily utilized in microcomputers, workstations, and high-performance computing environments. Their processing power is well-suited for applications such as high-speed data processing, CAD/CAM operations, multitasking, and multiuser systems. However, in industrial control applications, 8-bit microprocessors continue to dominate and are unlikely to be replaced by their 32-bit and 64-bit counterparts soon.

## i Why High-End Processors Are Not Ideal for Teaching Basic Concepts?

Focusing on high-end Intel 32-bit and 64-bit processors for introductory microprocessor education is impractical. This situation can be compared to using large-scale integrated (LSI) devices to teach fundamental logic gate concepts such as AND, NAND, and OR. A simpler processor with a well-defined instruction set is required to grasp the fundamental principles of microprocessor architecture and programming.

The Intel high-end processors are too complex for introductory courses due to their intricate architecture and extensive instruction set. These processors are primarily designed to support high-level programming languages, handle large databases, and process graphics-intensive applications. Their primary use is in personal computers (PCs) and network servers, where advanced computing power is essential. As a result, for fundamental microprocessor education, a simpler, more structured processor such as the 8-bit microprocessor is a far better choice.

# 2. The Microprocessor as a Programmable Device

A microprocessor is a programmable device, meaning it can be instructed to perform specific tasks within its operational limits. Much like a piano, which produces different tones depending on the keys pressed, a microprocessor processes and executes binary instructions according to a predefined set of rules. A musician selects keys based on a musical score, while a programmer selects and sequences instructions to control the microprocessor. The microprocessor is a versatile computing unit, capable of executing both complex computational functions and simple control tasks, such as turning devices on or off. By programming appropriate instructions, users can direct the microprocessor to process data and perform designated operations efficiently.

The tasks a microprocessor can execute are determined by its architecture and instruction set, which are defined by hardware engineers during the design phase. Engineers develop the logic circuits necessary for executing specific operations and establish a predefined instruction set that the processor understands. For example, a basic instruction for adding two numbers may be represented as an 8-bit binary code, such as 1000 0000. These instructions, composed of 0s and 1s, form the fundamental commands that a programmer selects and sequences to execute a given task. The execution order of these instructions is stored in memory, allowing the microprocessor to retrieve, interpret, and process them as needed.

In a computing system, software consists of a set of instructions or commands that enable a programmable device to perform a specific task. Hardware, on the other hand, refers to the physical components of a system that execute and support software operations. While

hardware provides the foundation for computational processes, it remains inactive without software. Software acts as the bridge between the user and the machine, ensuring that hardware resources are utilized effectively. A computing system requires integration of both software and hardware to function efficiently.

## i The microprocessor as a CPU (MPU)

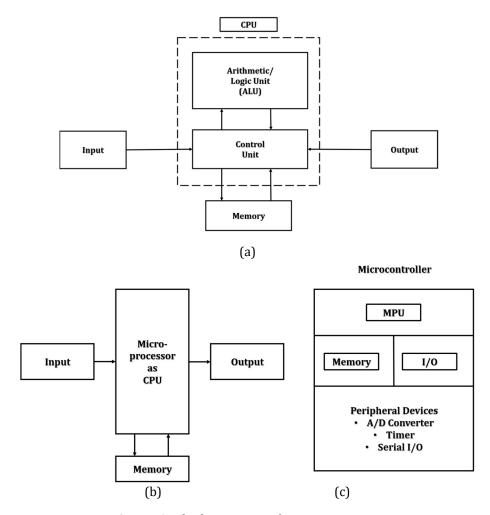

The microprocessor serves as the core component of a computer system. Traditionally, computers are represented by a block diagram comprising four fundamental components: memory, input, output, and the central processing unit (CPU). The CPU includes key functional elements such as the arithmetic and logic unit (ALU), control unit, registers, instruction decoders, counters, and control lines. The CPU retrieves instructions from memory, processes them, and executes tasks accordingly. It interacts with input/output devices (peripherals) to either receive or transmit data. While the CPU is responsible for managing communication between different components, the control unit coordinates the timing and execution of these operations.

Figure 1. Block Diagram of Microcomputer.

During the late 1960s, CPUs were built using discrete components mounted on multiple circuit boards. The advent of integrated circuit (IC) technology revolutionized CPU design, allowing it to be integrated into a single chip, leading to the development of the microprocessor. This advancement replaced the traditional multi-board CPU architecture with a compact microprocessor-based system. A computer system utilizing a

microprocessor as its CPU is called a microcomputer. The terms microprocessor and microprocessor unit (MPU) are often used interchangeably. The MPU functions as a complete processing unit with built-in control signals. However, due to the limited number of pins on a microprocessor chip, some control and multiplexed signals must be generated using additional external circuits to create a fully functional MPU.

## ii Evolution of Microprocessors

Microprocessors have undergone remarkable advancements since their inception. The first commercially available microprocessor, the Intel 4004, was introduced in 1971. It was a 4-bit processor primarily designed for calculators and other fundamental computing applications. This was soon followed by the Intel 8008, an 8-bit microprocessor, which expanded the scope of microprocessor applications beyond simple arithmetic processing. The introduction of the Intel 8080 and its enhanced version, the Intel 8085, represented a significant milestone in microprocessor development. These processors significantly improved computing capabilities, enabling microprocessors to be widely adopted in various computer systems. As technology progressed, the industry moved towards 16-bit, 32-bit, and 64-bit microprocessors, each offering greater processing power, enhanced memory addressing, and more efficient instruction execution.

## iii Technological Advancements in Microprocessors

Continuous improvements in microprocessor technology have resulted in higher clock speeds, lower power consumption, and greater functional integration. Modern microprocessors incorporate floating-point arithmetic units, cache memory, and multiple processing cores, allowing more efficient and high-speed computation. The introduction of parallel processing, artificial intelligence acceleration, and advanced power management has further expanded the capabilities of microprocessors. Today, they play a crucial role in diverse fields, from personal computing and industrial automation to embedded systems and artificial intelligence applications. The evolution of microprocessors continues, driving innovation in computing and digital systems worldwide.

**Table 1** Intel Microprocessors Historical Perspective

| Processor | Year of<br>Introduction | Number of<br>Transistors | Initial<br>Clock<br>Speed | Address<br>Bus | Data<br>Bus | Addressable<br>Memory |

|-----------|-------------------------|--------------------------|---------------------------|----------------|-------------|-----------------------|

| 4004      | 1971                    | 2,300                    | 108<br>kHz                | 10-bit         | 4-bit       | 640 bytes             |

| 8008      | 1972                    | 3,500                    | 200<br>kHz                | 14-bit         | 8-bit       | 16 K                  |

| 8080      | 1974                    | 6,000                    | 2 MHz                     | 16-bit         | 8-bit       | 64 K                  |

| 8085      | 1976                    | 6,500                    | 5 MHz                     | 16-bit         | 8-bit       | 64 K                  |

| 8086      | 1978                    | 29,000                   | 5 MHz                     | 20-bit         | 16-bit      | 1 M                   |

| 8088      | 1979                    | 29,000                   | 5 MHz                     | 20-bit         | 8-bit       | 1 M                   |

| 80286     | 1982                    | 134,000                  | 8 MHz                     | 24-bit         | 16-bit      | 16 M                  |

| 80386          | 1985 | 275,000 | 16<br>MHz  | 32-bit | 32-bit        | 4 G  |

|----------------|------|---------|------------|--------|---------------|------|

| 80486          | 1989 | 1.2 M   | 25<br>MHz  | 32-bit | 32-bit        | 4 G  |

| Pentium        | 1993 | 3.1 M   | 60<br>MHz  | 32-bit | 32/64-<br>bit | 4 G  |

| Pentium<br>Pro | 1995 | 5.5 M   | 150<br>MHz | 36-bit | 32/64-<br>bit | 64 G |

| Pentium II     | 1997 | 8.8 M   | 233<br>MHz | 36-bit | 64-bit        | 64 G |

| Pentium III    | 1999 | 9.5 M   | 650<br>MHz | 36-bit | 64-bit        | 64 G |

| Pentium 4      | 2000 | 42 M    | 1.4<br>GHz | 36-bit | 64-bit        | 64 G |

# 3. Organization of a Microprocessor-Based System

A microprocessor-based system consists of essential components that work together to execute computing and control tasks efficiently. Figure 2 illustrates a simplified yet formal structure of such a system. Since a microcomputer is a type of microprocessor-based system, it follows the same fundamental architecture. The core components of this system include the microprocessor, input/output (I/O) devices, and memory (both read/write memory and read-only memory). These elements are interconnected through a shared communication channel known as the system bus, which facilitates the transfer of data, addresses, and control signals. The entire system, comprising these interconnected components, is referred to as a microcomputer system, with each individual component serving as a subsystem within it.

It is important to distinguish between the terms microprocessor and microcomputer, as they are often used interchangeably in popular literature. The microprocessor is a single component within a system, functioning as the central processing unit (CPU). It performs computations, logic operations, and control functions necessary for system execution. In contrast, a microcomputer is a complete computing system, integrating the microprocessor along with memory, input/output interfaces, and supporting circuits to form a fully operational computing unit.

Additionally, the term peripheral refers to input/output (I/O) devices connected to the microcomputer. These devices, such as keyboards, displays, storage units, and sensors, enable interaction between the user and the computing system. The organization of these components in a microprocessor-based system or microcomputer is depicted in Figure 2, providing a structural representation of how they interact to execute programmed instructions. Each component within this structure plays a crucial role in ensuring efficient data processing, system control, and external communication, making microprocessor-based systems essential in modern computing and automation applications.

**Figure 2** Microprocessor-Based System with Bus Architecture.

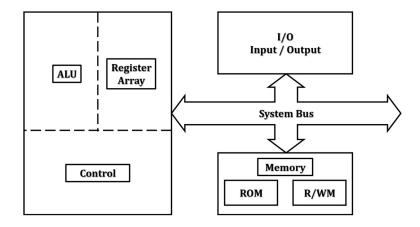

## i Microprocessor Internal blocks

A microprocessor is a clock-driven semiconductor device composed of electronic logic circuits fabricated using Large-Scale Integration (LSI) or Very-Large-Scale Integration (VLSI) technology. It serves as the processing core of a system, performing various computing operations and executing instructions to make decisions that alter the sequence of program execution. In large computing systems, the CPU consists of multiple components spread across one or more circuit boards. However, in a microprocessor, all essential logic circuits, including the Control Unit (CU), Arithmetic Logic Unit (ALU), and Register Array, are integrated onto a single chip, making it a compact and efficient computing device. For better understanding, the internal architecture of a microprocessor can be divided into three main functional units, as depicted in Figure 2.

Arithmetic and Logic Unit (ALU): The Arithmetic and Logic Unit (ALU) is the computational core of the microprocessor. It executes arithmetic operations such as addition, subtraction, increment, and decrement and performs logical operations including AND, OR, XOR, and bitwise shifts. The ALU interacts with registers and memory to process data, and the results of operations affect specific status flags in the flag register, indicating conditions such as zero, carry, parity, and sign.

**Register Array:** The register array consists of multiple temporary storage locations, known as registers, that facilitate fast data access and manipulation. These registers are classified into general-purpose registers and special-purpose registers:

General-Purpose Registers (B, C, D, E, H, and L) – Used for storing intermediate results and operands during instruction execution.

Accumulator (A Register) – A dedicated register where most arithmetic and logical operations take place.

Flag Register – Holds status flags to indicate the outcome of ALU operations.

Program Counter (PC) – Keeps track of the next instruction to be executed.

Stack Pointer (SP) – Points to the top of the stack, used for temporary data storage and function calls.

<u>Control Unit (CU):</u> The Control Unit (CU) acts as the brain of the microprocessor, generating timing and control signals to coordinate all system operations. It ensures

proper data flow between the ALU, register array, memory, and peripheral devices. The control unit manages instruction decoding, execution sequencing, and communication with external components through control signals such as Read ( $R\bar{D}$ ), Write ( $W\bar{R}$ ), and Address Latch Enable (ALE).

#### ii Memory

Memory is an essential component of a microprocessor-based system, responsible for storing binary information, including instructions and data, and supplying it to the microprocessor when needed. The microprocessor retrieves instructions and data from memory to execute programs and performs the necessary computing operations in its Arithmetic and Logic Unit (ALU). The results of these operations are either sent to the output devices for display or stored back in memory for future use. As shown in Figure 3, the memory block is typically divided into two main sections:

- 1. Read-Only Memory (ROM): Read-Only Memory (ROM) is used for storing programs that do not require modifications. Programs stored in ROM are permanent and can only be read, not altered. A common example is the monitor program in a single-board microcomputer, which interprets user inputs from a keyboard and converts them into binary instructions for the microprocessor. Since ROM retains its contents even when power is turned off, it is classified as non-volatile memory.

- 2. Random-Access Memory (RAM): Read/Write Memory (R/WM), commonly referred to as Random-Access Memory (RAM), is used for storing user programs and data during execution. Unlike ROM, the contents of RAM can be read and modified. This memory is often called user memory because it temporarily holds instructions and data entered by the user. In single-board microcomputers, a monitor program tracks inputs from a hexadecimal keypad and stores the corresponding instructions and data in RAM. Since RAM is volatile memory, its contents are lost when the power supply is turned off.

# iii Input/Output devices

The Input/Output (I/O) subsystem is the third essential component of a microprocessor-based system, responsible for enabling communication between the microprocessor and the external world. I/O devices, also known as peripherals, serve as an interface between the user and the system, allowing data and instructions to be transferred to and from the microprocessor.

**Input Devices:** Input devices allow the transfer of binary information, such as data and instructions, from external sources into the microprocessor. Common input devices include:

Keyboards – Used to enter data and commands.

Switches – Simple input mechanisms that provide binary signals to the microprocessor.

Analog-to-Digital (A/D) Converters – Convert analog signals (e.g., temperature, pressure) into digital form for processing.

In laboratory microcomputers, input is typically provided through a hexadecimal (Hex) keyboard or an ASCII keyboard:

Hexadecimal Keyboard – A 16-key keypad (digits 0-9 and A-F) with additional function keys for storing data and executing programs.

ASCII Keyboard – Similar to a typewriter keyboard, used for entering programs in an English-like language. While ASCII keyboards are common in personal computers (PCs), single-board microcomputers often use Hex keyboards. Microprocessor-based consumer products, such as microwave ovens, frequently feature decimal keypads for user input.

<u>**Output Devices:**</u> Output devices transfer processed data from the microprocessor to the external world. These devices include:

Light-Emitting Diodes (LEDs) – Used for basic binary indication and status displays.

Seven-Segment Displays – Display numerical values and simple characters.

Cathode-Ray Tube (CRT) or Video Screen – Found in traditional computing systems for visual output.

Printers – Used to produce hard copies of processed data.

Digital-to-Analog (D/A) Converters – Convert digital signals from the microprocessor into analog signals for real-world applications.

#### iv System Bus

The system bus is a communication path between the microprocessor and peripherals; it is nothing but a group of wires that carry bits. Several buses in the system will be discussed in the next chapter. All peripherals (and memory) share the same bus; however, the microprocessor communicates with only one peripheral at a time. The control unit of the microprocessor provides timing.

## 4. Microcomputer Organization:

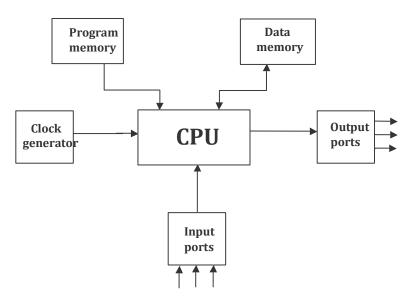

A microprocessor combined with memory and input/output devices forms a microcomputer. These components are shown in the figure below:

Figure 3 Basic Components of Microcomputer

# Central Processing Unit (CPU) and Program Execution in a Microprocessor-Based System

The Central Processing Unit (CPU) is the core of a microprocessor-based system and is responsible for executing instructions and processing data. It consists of three major components: Arithmetic and Logic Unit (ALU): Performs arithmetic operations such as addition, subtraction, multiplication, and division, as well as logical operations like AND, OR, XOR, and NOT. Register Unit: Contains various temporary storage locations (registers) used for storing data, intermediate results, and special-purpose information such as the program counter (PC), stack pointer (SP), and flag registers.

<u>Control Unit (CU)</u>: Generates necessary timing and control signals to coordinate operations between the CPU, memory, and peripheral devices. The CPU fetches instructions from program memory (ROM or RAM), retrieves data from data memory or an input device, processes the data using the ALU, and then stores the result in memory or sends it to an output device.

<u>System Boot-Up and Reset Mechanism</u>: When power is turned on, the monitor program stored in EPROM or ROM initializes the system. The Reset key is used to clear the program counter (PC), which then holds the memory address 0000H. Some systems feature automatic power-on reset, which ensures the system starts from a predefined state every time it is powered on. Upon resetting, the program counter (PC) places address 0000H on the address bus, and the instruction stored at that location is fetched and executed. This marks the beginning of the Key Monitor program, which is usually stored on page 00H of memory.

## **Low-Level Languages**

Low-level languages are programming languages that are closer to machine language and provide direct hardware control.

*Machine Language*: Uses binary code (0s and 1s) directly understood by the microprocessor. Difficult to write, read, and debug. Example: 10110000 01100001 (Binary representation of MOV A, 61H in 8085).

*Assembly Language*: Uses mnemonics instead of binary code. It is easier to understand than machine language but still hardware dependent. Requires an assembler for conversion to machine code.

## **High-Level Languages**

High-level languages (HLLs) are programming languages that use English-like syntax and abstraction, making them easier for humans to understand. They are hardware-independent and require a compiler or interpreter to convert them into machine code. Examples: C,

# Python, Java, FORTRAN

Advantages: Easy to learn and use. Portable across different hardware architectures. Requires less knowledge of hardware details.

int a = 5, b = 10;

int sum = a + b:

This code is much easier to understand than low-level assembly instructions.

**Table 2** Comparison of languages

| Feature                | Machine<br>Language | Assembly<br>Language    | High-Level Language         |

|------------------------|---------------------|-------------------------|-----------------------------|

| Readability            | Difficult (binary)  | Moderate<br>(mnemonics) | Easy (English-like)         |

| Execution Speed        | Fastest             | Faster                  | Slower (due to compilation) |

| Hardware<br>Dependence | Highly dependent    | Dependent               | Independent                 |

| Ease of Debugging      | Difficult           | Moderate                | Easy                        |

Steps in writing and executing an assembly language program

# **Step 1: Writing Instructions in Mnemonics**

The assembly language program is written using mnemonics obtained from the instruction set of the microprocessor. Mnemonics are human-readable representations of machine instructions.

# Step 2: Finding Hexadecimal Machine Code

Each mnemonic corresponds to a hexadecimal opcode in the microprocessor's instruction set. The assembler or manual lookup can be used to convert mnemonics into machine code.

## Step 3: Entering the Program into Memory

The program is loaded into the user memory sequentially. A Hexadecimal Keyboard (or a system loader) is used to input the machine code into the microprocessor's memory.

# Step 4: Executing the Program

The program is executed by pressing the Execute key or using a command in an emulator/software tool. The microprocessor fetches, decodes, and executes each instruction.

The result is stored in a register or displayed on LEDs/LCD (if interfaced with the microprocessor system).

## i ALU (Arithmetic and Logic Unit)

This unit performs computing functions on m-bit data where 'm' is the bit size of the processor. These functions are arithmetic operations such as addition, subtraction and logical operation such as AND, OR, XOR, rotate, compare etc. Results are stored either in registers or in memory or sent to output devices.

## ii Register Unit:

It contains various 8-bit or 16-bit registers. These registers are used primarily to store data temporarily during the execution of a program. Some of the registers are accessible to the user through instructions. It means their contents can be read and/or changed through instructions. Some of the registers are not accessible to user but they are used by the processor for the execution of an instruction. 8085A microprocessor contains 8-bit registers such as Accumulator (Reg. A), B, C, D, E, H, L etc. and 16-bit registers such as Program Counter (PC), Stack Pointer (SP).

The Program Counter (PC) is a 16-bit register that holds the address of the next instruction to be executed. The PC fetches the address of the instruction from memory. After fetching, it automatically increments to point to the next instruction. In the case of jump or call instructions, the PC is modified to point to a new address. Controls the sequence of execution in a program.

The Stack Pointer (SP) is a 16-bit register that holds the address of the top of the stack in memory. The stack is used for temporary storage of data, return addresses, and registers. The SP is decremented (decreases) when data is pushed (stored) onto the stack. The SP is incremented (increases) when data is popped (retrieved) from the stack. It works in LIFO (Last In, First Out) order. The SP decreases by 2 during PUSH instruction and increases by 2 during POP instruction.

## iii Timing and Control Unit:

It provides necessary timing & control signals required for the operation of microcomputer. It controls the flow of data between the microprocessor and peripherals (input, output & memory). The control unit gets a clock signal which determines the speed of the microprocessor. In all, the CPU has the following basic functions:

## 5. Memory

Memory plays a crucial role in a microprocessor-based system, as it stores both program instructions and data needed for execution. It consists of two main types: Read-Only Memory (ROM) and Read/Write Memory (RWM), both of which are considered Random Access Memory (RAM) since data can be accessed from any location directly.

- 1. <u>Read-Only Memory</u> (ROM): ROM (Read-Only Memory) is a non-volatile memory, meaning its contents remain intact even when the power is turned off. Since ROM is read-only, data stored in it cannot be modified after manufacturing (except in the case of programmable ROMs like EPROM or EEPROM). ROM is typically used for storing fixed programs that do not change during system operation. One common use of ROM is in microcomputers, where it stores the monitor program—a set of instructions that initializes the system and handles user interactions. This ensures that the processor starts executing from a predetermined location when the system powers up or is reset.

- 2. <u>Read/Write Memory</u>: RWM (Read/Write Memory), often referred to as RAM (Random Access Memory), is a volatile memory that loses its contents when power is turned off.

Unlike ROM, RWM allows both reading and writing of data, making it essential for storing user programs, temporary data, and intermediate results during program execution.

During a memory read operation, the microprocessor retrieves data from a specific location without altering its contents. During a memory write operation, new data is stored in a specified location, overwriting the previous contents.

#### i Program Memory:

The program memory is responsible for storing the sequence of instructions that the CPU executes. When a microcomputer system starts up, either on power-up or after a reset, the processor fetches and executes instructions from a predetermined location in program memory. Since the program remains fixed and does not change during execution, it is typically stored in ROM. The first instruction of the program must be placed at the processor's predefined reset address to ensure proper execution.

#### ii Data Memory:

Data memory is used for storing variables, intermediate results, and temporary data needed for program execution. It enables the microprocessor to manipulate data according to the algorithm provided in the program instructions. Internal Registers: Microprocessors have small internal memory in the form of registers, which store frequently used data and improve processing speed. External Data Memory: If the storage requirement exceeds the capacity of internal registers, the system uses external RAM for additional data storage.

# 6. Microcomputer Bus System

A microcomputer consists of three essential buses that facilitate the transfer of address, data, and control signals required for program execution. These buses serve as communication pathways that connect the microprocessor, memory, and input/output (I/O) devices, enabling seamless data exchange and coordinated operations. The efficiency of a microcomputer heavily depends on the organization and performance of these buses, as they determine how quickly and effectively instructions and data are transmitted between system components.

# i Address Bus

In a microcomputer system, the central processing unit (CPU) is the core component responsible for controlling system operations. When executing a program, the CPU determines which device (memory or an I/O peripheral) should participate in a data transfer. This selection is accomplished by placing the specific address of the target device onto the address bus. The address bus is unidirectional, meaning that the flow of address information occurs only from the microprocessor to memory or I/O devices. The CPU transmits an address to identify a specific memory location or an I/O device before initiating a data transfer. In the case of memory access, the address bus not only identifies the memory device but also specifies the exact memory location within it.

The size of the address bus determines the number of addressable memory locations. For instance, an 8-bit address bus can address  $256 (2^8)$  memory locations, whereas a 16-bit address bus, as seen in the 8085 microprocessor, can address  $64 \text{ KB} (2^{16})$  of memory space.

As microprocessors evolve, they incorporate wider address buses, enabling access to larger memory capacities and more complex I/O devices. In modern computing systems, memory management techniques, such as paging and segmentation, allow efficient utilization of the address bus, enabling microprocessors to address vast amounts of memory beyond their physical addressing limit. Additionally, the introduction of multiplexed address buses in some microprocessors optimizes pin usage, further enhancing the design of compact and efficient computing devices.

#### ii Data Bus in Microcomputer Systems

The data bus is a set of lines used to transfer data between the microprocessor, memory, and peripheral devices. In the 8085A microprocessor, the data bus consists of 8 lines (D7-D0), which allow the processor to handle 8-bit data transfers at a time. The data bus is a shared resource, meaning that multiple devices can connect to it. However, to avoid conflicts, only one device should transmit data at any given time, while all other devices must remain in a high-impedance (high-Z) state to prevent electrical interference.

Unlike the address bus, which is unidirectional, the data bus is bidirectional, meaning data can flow both to and from the microprocessor. This bidirectional nature allows the processor to read data from memory or I/O devices and write data back when required. Therefore, this is called bidirectional data bus (BDB). In some microprocessors, the data pins are also used to send other information such as address bits in addition to data. This means that the data pins are time shared or multiplexed. In Intel 8085A microprocessor lower 8-bits of the address (A7-A0) are time-multiplexed with the 8-bit data (D7-D0) and, therefore, this bus is called AD bus (AD7-AD0).

In some microprocessors, data pins serve multiple purposes, such as transmitting both address and data signals. This technique is known as multiplexing and helps optimize the number of available pins on the microprocessor. For example, in the Intel 8085A microprocessor, the lower 8 bits of the address bus (A7-A0) are multiplexed with the 8-bit data bus (D7-D0), forming the AD bus (AD7-AD0). During the first phase of an operation, these lines carry the address, and in the second phase, they are used for data transfer. To separate address and data signals, external latching circuits are employed, such as the 74LS373 latch.

#### iii Control Bus

The control bus consists of a set of dedicated control signals that coordinate operations between the microprocessor, memory, and I/O devices. These signals synchronize data transfers, ensuring that all system components operate in a coordinated manner. Every operation performed by the microprocessor, such as reading from memory, writing to memory, or communicating with I/O devices, is controlled through signals transmitted via the control bus. Some of the signals of the control bus are issued by the processor and some of the signals are received by the processor. Therefore, the control bus is called bidirectional control bus (BCB). The difference between BDB and BCB is that in BDB all data lines are either in input mode or in output mode whereas in BCB the direction of signal flow on a line is fixed.

# Common control signals in the 8085 microprocessor include:

$R\bar{D}$  (Read signal): Indicates that the microprocessor is reading data from memory or an I/O device.

$W\bar{R}$  (Write signal): Indicates that the microprocessor is writing data to memory or an I/O device.

$IO/\bar{M}$  (Memory or I/O selection): Differentiates between memory ( $IO/\bar{M}=0$ ) and I/O operations ( $IO/\bar{M}=1$ ).

The control bus is bidirectional, meaning that some signals are generated by the processor, while others are received from external devices. Unlike the bidirectional data bus, where all lines function as either inputs or outputs at a given time, the control bus features fixed-direction signals, ensuring consistent communication between system components. As microprocessor technology has advanced, additional control signals have been introduced to manage interrupt handling, direct memory access (DMA), and power-saving features, enhancing the efficiency of modern computing systems.

# Chapter 2. 8085 Architecture and Pin Diagram

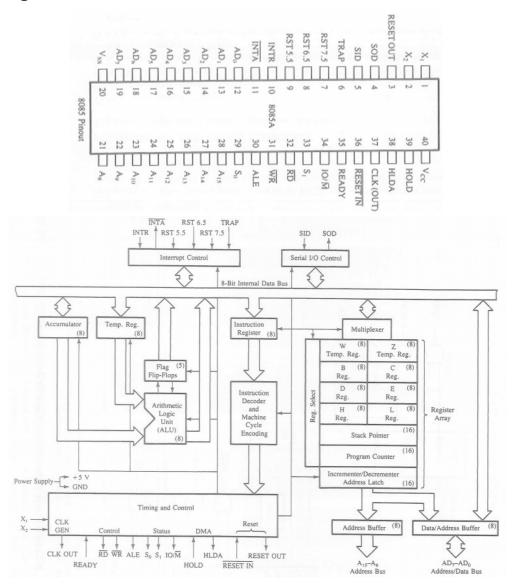

The 8085 microprocessor, developed by Intel in 1976, is an 8-bit microprocessor designed for general-purpose computing and embedded applications. It follows the Von Neumann architecture, meaning that both data and instructions share the same memory space. The processor operates on a +5V power supply and runs at a clock speed of 3 MHz with a 16-bit address bus, it can access 64 KB of memory, while its 8-bit data bus allows processing of 8-bit data at a time.

The 8085 architecture is divided into several functional units, including the Arithmetic and Logic Unit (ALU), Register Array, Control Unit, Address and Data Bus, and Interrupt System. These components work together to execute instructions efficiently.

## 1. Internal Architecture of 8085

The internal structure of the 8085 microprocessor consists of the following key units:

## i Arithmetic and Logic Unit (ALU)

The Arithmetic and Logic Unit (ALU) is responsible for performing arithmetic operations such as addition, subtraction, and logical operations such as AND, OR, and XOR. The ALU interacts with the accumulator and other registers to execute these operations efficiently. It also affects the status flags stored in the flag register.

#### ii Register Array

The 8085 microprocessor contains a set of registers that store data temporarily during execution. These include six general-purpose registers (B, C, D, E, H, and L), an accumulator (A), a program counter (PC), and a stack pointer (SP). The registers can be used individually or in pairs (BC, DE, HL) for 16-bit operations. The accumulator is an essential register used for arithmetic and logical operations.

## **Different Types of Registers in 8085**

The 8085 microprocessor has several registers used for data storage, processing, and control operations. These registers can be classified based on their size, function, and accessibility.

1. Classification Based on Size

8-bit Registers: Accumulator (A), General-purpose registers (B, C, D, E, H, L), Flag register 16-bit Registers: Program Counter (PC), Stack Pointer (SP)

2. Classification Based on Functionality

## **General-Purpose Registers**

Registers B, C, D, E, H, and L are used for temporary data storage and arithmetic operations. They can be used as register pairs (BC, DE, HL) for 16-bit operations.

## Special-Purpose Registers

Accumulator (A): An 8-bit register used for arithmetic and logic operations. It stores the final result of computations.

Flag Register: Stores the status of operations with five flags – Sign (S), Zero (Z), Auxiliary Carry (AC), Parity (P), and Carry (CY).

# **Control and Addressing Registers**

Program Counter (PC): A 16-bit register that holds the memory address of the next instruction to be executed. It is automatically incremented after each instruction fetch.

Stack Pointer (SP): A 16-bit register that keeps track of the top of the stack during subroutine calls and interrupts.

# 3. Classification Based on User Accessibility

User-Accessible Registers: Accumulator (A), General-purpose registers (B, C, D, E, H, L)

System-Controlled Registers: Program Counter (PC), Stack Pointer (SP), Flag Register

#### iii Control Unit

The control unit is responsible for generating control signals to manage data flow between the microprocessor, memory, and peripherals. It interprets instructions fetched from memory and coordinates the operations of the ALU and registers. Control signals include  $R\bar{D}$  (Read),  $W\bar{R}$  (Write),  $IO/\bar{M}$  (Memory or I/O selection), and ALE (Address Latch Enable).

# 2. Pin Diagram and Functions of Various Pins

Figure 4 Pin diagram and functional block diagram.

The 8085 microprocessor has a 40-pin dual in-line package (DIP) configuration. The pins are categorized into different groups based on their functions, such as power supply, clock signals, control signals, data and address buses, and serial I/O.

# i Power Supply and Clock Signals

- VCC (Pin 40): +5V power supply.

- GND (Pin 20): Ground.

- X1, X2 (Pins 1, 2): Crystal oscillator connections for clock generation.

- CLK OUT (Pin 37): Provides clock signals to external peripherals.

8085 has a clock generation circuit on the chip but an external quartz crystal or L C circuit or RC circuit should be connected at pins X1 and X2. The maximum internal clock frequency of 8085 is 3.07 MHz

#### ii Address and Data Buses

- Address Bus (A15–A8): The higher-order address lines (A15–A8) are used for memory addressing.

- Multiplexed Address/Data Bus (AD7–AD0): The lower-order address and data lines are multiplexed to save pins. During the address phase, these lines carry address bits, and during the data phase, they carry data.

#### iii Control and Status Signals

- RD (Pin 32): Read signal, active low, used to read data from memory or I/O.

- WR (Pin 31): Write signal, active low, used to write data to memory or I/O.

- IO/M (Pin 34): Distinguishes between memory (0) and I/O (1) operations.

- ALE (Pin 30): Address Latch Enable, used to demultiplex address/data lines.

- READY (Pin 35): Indicates whether the peripheral is ready for data transfer.

# Pins in the Timing and Control Unit of the 8085 Microprocessor

The 8085 microprocessor has several pins associated with the timing and control unit that manage data flow, memory access, and I/O operations. These pins are crucial for coordinating the execution of instructions.

**Table 3** Key Pins and Their Functionality

| Pin                                     | Туре   | Function                                                                                    |

|-----------------------------------------|--------|---------------------------------------------------------------------------------------------|

| CLK (Clock Out)                         | Output | Provides system clock to synchronize external devices.                                      |

| RD (Read Control Signal)                | Output | Indicates that data is being read from memory or I/O device.                                |

| WR (Write Control Signal)               | Output | Indicates that data is being written to memory or an I/O device.                            |

| ALE (Address Latch Enable)              | Output | Used to separate the lower byte of address from the multiplexed address/data bus (AD0-AD7). |

| IO/M (Input/Output or<br>Memory Select) | Output | Distinguishes between memory (0) and I/O (1) operations.                                    |

| Pin                                                | Туре   | Function                                                                                                         |

|----------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------|

| S <sub>0</sub> and S <sub>1</sub> (Status Signals) | Output | Indicate the operation type (Fetch, Memory Read, Memory Write, I/O Read, I/O Write, or Halt).                    |

| READY                                              | Input  | Ensures synchronization with slow memory or I/O devices by pausing the microprocessor until the device is ready. |

| RESET IN                                           | Input  | When activated, resets the microprocessor and restarts execution from address 0000H.                             |

| RESET OUT                                          | Output | Used to reset external devices upon system reset.                                                                |

The timing and control unit in the 8085 microprocessor plays a critical role in data flow, memory access, and I/O operations. These control signals help in synchronizing the processor with external memory, I/O devices, and other components.

## iv Interrupts and Serial I/O

- TRAP, RST7.5, RST6.5, RST5.5, INTR: Hardware interrupts.

- Serial Input/Output: SID (Serial Input Data) and SOD (Serial Output Data) for serial communication.

# **Interrupt Signals in 8085 Microprocessor**

The 8085 microprocessor has five interrupt signals that allow external devices to interrupt the normal execution of a program. These interrupts help in handling urgent tasks, external events, and I/O operations.

**Table 4** List of Interrupt Signals in 8085

| Interrupt | Туре             | Priority | Vector Address                                         | Maskable | Triggering Method           |

|-----------|------------------|----------|--------------------------------------------------------|----------|-----------------------------|

| TRAP      | Non-<br>maskable | Highest  | 0024Н                                                  | No       | Edge and Level<br>Triggered |

| RST 7.5   | Maskable         | Second   | 003CH                                                  | Yes      | Edge Triggered              |

| RST 6.5   | Maskable         | Third    | 0034Н                                                  | Yes      | Level Triggered             |

| RST 5.5   | Maskable         | Fourth   | 002CH                                                  | Yes      | Level Triggered             |

| INTR      | Maskable         | Lowest   | Any memory<br>location (needs<br>external<br>hardware) | Yes      | Level Triggered             |

Interrupt Priority Order: TRAP > RST 7.5 > RST 6.5 > RST 5.5 > INTR

The Software interrupts are program instructions. These instructions are inserted at desired locations in a program. While running a program, if software interrupt instruction is encountered then the processor executes an interrupt service routine. If an interrupt is

initiated in a processor by an appropriate signal at the interrupt pin, then the interrupt is called Hardware interrupt. The Software interrupt is initiated by the main program, but the Hardware interrupt is initiated by an external device. In 8085, the Software interrupt cannot be disabled or masked but the Hardware interrupt except TRAP can be disabled or masked. When an interrupt is accepted, if the processor control branches to a specific address defined by the manufacturer, then the interrupt is called vectored interrupt. In non-vectored interrupt there is no specific address for storing the interrupt service routine. Hence the interrupted device should give the address of the interrupt service routine.

Masking is preventing the interrupt from disturbing the current program execution. When the processor is performing an important job (process) and if the process should not be interrupted then all the interrupts should be masked or disabled. In processor with multiple interrupts, the lower priority interrupt can be masked to prevent it from interrupting, the execution of interrupt service routine of higher priority interrupt. The processor keeps on checking the interrupt pins at the second T -state of the last Machine cycle of every instruction. If the processor finds a valid interrupt signal and if the interrupt is unmasked and enabled, then the processor accepts the interrupt. The acceptance of the interrupt is acknowledged by sending an OOA signal to the interrupted device. The interrupts of 8085 except TRAP are disabled after anyone of the following operations—

- **1**. Executing Dl instruction.

- **2**. System or processor reset.

- **3**. After reorganization (acceptance) of an interrupt.

For the interrupt INTR, the interrupting device has to place either an RST opcode or CALL opcode followed by l6-bit address. Instruction RST opcode is placed then the corresponding vector address is generated by the processor. In the case of CALL Opcode the given l6-bit address will be the vector address.

# v Generating Control Signals

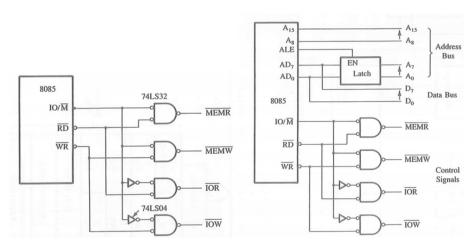

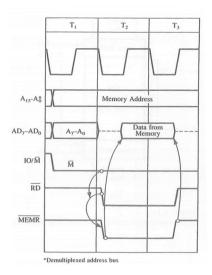

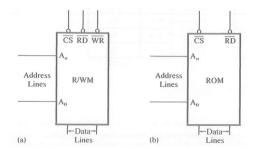

Figure below shows the  $\overline{\text{RD}}$  (Read) as a control signal. Because this signal is used both for reading memory and for reading an input device, it is necessary to generate two different Read signals: one for memory and another for input. Similarly, two separate Write signals must be generated.

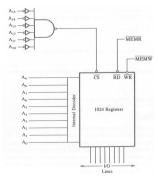

The figure below shows that four different control signals are generated by combining the signals  $\overline{RD}$ ,  $\overline{WR}$ , and  $IO/\overline{M}$ . The signal  $IO/\overline{M}$  goes low for the memory operation. When both input signals go low, the outputs of the gates go low and generate MEMR (Memory Read) and MEMW (Memory Write) control signals. When the  $IO/\overline{M}$  signal goes high, it indicates the peripheral I/O operation.

Figure 5: Generation of control signal for interfacing.

# 3. System Bus (Address Bus, Data Bus, and Control Bus)

The 8085 microprocessor communicates with memory and peripheral devices using the system bus, which consists of three main components: the Address Bus, Data Bus, and Control Bus.

#### i Address Bus

The address bus is used to specify the memory location or I/O device to be accessed. It is 16-bit wide, allowing the microprocessor to address up to 64 KB of memory ( $2^{16}$  locations). The address bus is unidirectional, meaning data flows only from the microprocessor to memory.

#### ii Data Bus

The data bus is used to transfer data between the microprocessor, memory, and I/O devices. It is 8-bit wide, meaning the microprocessor can process 8-bit data at a time. The data bus is bidirectional, allowing data to flow in both directions.

## iii Control Bus

The control bus consists of signals used to control data transfer. These signals include  $R\bar{D}$  (Read),  $W\bar{R}$  (Write),  $IO/\bar{M}$  (Memory/I/O selection), and ALE (Address Latch Enable). The control bus ensures proper synchronization between the microprocessor and external devices.

Additionally, many peripheral device operations require direct hardware interaction, which is often not supported by high-level languages. For example, operations involving serial communication, direct memory access (DMA), and device-specific control registers are typically implemented using assembly language. As a result, even in modern computing, assembly language remains an essential tool for system programming, embedded applications, and performance-critical tasks.

## 4. Data formats in computer

Data in digital systems is represented in different formats based on the application and processing requirements. The commonly used data formats are ASCII code, Extended ASCII, BCD code, Signed Integer, and Unsigned Integer.

## 1. ASCII Code (American Standard Code for Information Interchange)

ASCII (7-bit) is a standard character encoding format used to represent text on computers. It uses 7 bits to represent 128 characters (0-127), including letters, digits, punctuation, and

control characters.

'A' = 65 (Decimal) = 1000001 (Binary)

'a' = 97 (Decimal) = 1100001 (Binary)

'1' = 49 (Decimal) = 0110001 (Binary)

# 2. Extended ASCII Code (8-bit ASCII)

Extended ASCII (8-bit) extends the standard ASCII set to 256 characters (0-255). It includes special characters, graphical symbols, and accented letters.

'C' = 128 (Extended ASCII)

'é' = 130 (Extended ASCII)

# 3. BCD (Binary-Coded Decimal)

BCD represents decimal numbers (0-9) in 4-bit binary form. Each decimal digit is converted separately into 4-bit binary.

Decimal 25 → BCD: 0010 0101

Decimal  $93 \to BCD$ : 1001 0011

## 4. Signed Integer Representation

Signed integers represent both positive and negative numbers. The most common method is Two's Complement Representation, where:

MSB (Most Significant Bit) is the sign bit (0 = Positive, 1 = Negative).

Positive Numbers → Stored in normal binary.

Negative Numbers  $\rightarrow$  Stored in two's complement form.

+5 = 00000101, -5 = 11111011 (Two's Complement of 00000101)

Range for 8-bit Signed Integer: -128 to +127

## 5. Unsigned Integer Representation

Unsigned integers represent only positive numbers, using all available bits for magnitude.

Range for 8-bit Unsigned Integer: 0 to 255

**Table 5** Different data format and their properties

| Data Format | Bit Size | Range/Usage | Example         |

|-------------|----------|-------------|-----------------|

|             |          |             | (Binary         |

|             |          |             | Representation) |

| ASCII                    | 7-bit           | 128 characters | 'A' = 1000001, 'a'<br>= 1100001  |

|--------------------------|-----------------|----------------|----------------------------------|

| Extended ASCII           | 8-bit           | 256 characters | 'Ç' = 10000000                   |

| BCD                      | 4-bit per digit | 0-9 per digit  | 25 → 0010 0101                   |

| Signed Integer (8-bit)   | 8-bit           | -128 to +127   | +5 = 00000101, -<br>5 = 11111011 |

| Unsigned Integer (8-bit) | 8-bit           | 0 to 255       | 5 = 00000101,<br>255 = 11111111  |

# 5. Hardware Components in a Microcomputer-Based System

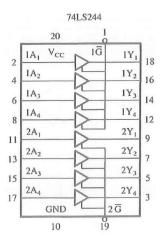

In addition to the 8085 microprocessor, a microcomputer-based system requires several supporting hardware components to ensure proper functionality and communication between system elements. These components include tri-state devices, buffers, latches, and decoders, which help in efficient data transfer and control.

**Tri-state devices** are essential in systems where multiple components share a common data bus. They have three output states: high (1), low (0), and high-impedance (Z). The high-impedance state effectively disconnects the device from the bus, preventing conflicts when multiple components attempt to transmit data simultaneously. **Buffers** act as intermediate circuits that amplify or regulate signals, ensuring reliable data transmission between the microprocessor and peripherals. They help in isolating circuits, preventing excessive current draw from the processor, and reducing loading effects on the bus.

Other essential components include latches, which temporarily hold data before it is transferred, and decoders, which help in memory and peripheral selection. These components collectively enhance the performance, stability, and efficiency of microcomputer-based systems by managing data flow and ensuring smooth interaction between the microprocessor, memory, and I/O devices.

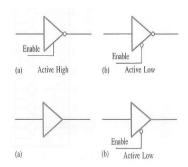

#### i Tri-State Devices